Repensant l’étage d’entrée numérique de nos convertisseurs, nous avons développé un procédé permettant l’élimination définitive du jitter issu de la source. En permettant aux circuits conversion de travailler de manière optimale, le SJR garantit une qualité de conversion numérique/analogique inégalée, quelque soit le format numérique d’entrée.

ELIMINER LA GIGUE A LA SOURCE

La gigue (ou jitter en anglais) contenue dans le signal d’entrée est source de distorsions lors de la conversion numérique/analogique, dues à un décalage de la référence temporelle entre chaque échantillon.

Nécessité d’une nouvelle approche

Pour contrer ce phénomène, deux technologies sont habituellement employées : L’utilisation de PLLs (boucles à verrouillage de phase) ou l’utilisation de ré-échantillonneurs asynchrones (ASRC).

Bien que ces deux technologies permettent d’atténuer l’influence du jitter source, elles sont incapables de s’en affranchir totalement. Dans le cas de l’utilisation d’une PLL, une partie du jitter source se retrouve dans l’horloge générée ; dans le cas de l’utilisation d’un ASRC, ne partie du jitter source se retrouve encodé dans le signal numérique généré.

D’autres artifices permettent d’améliorer la réjection du jitter, comme les « re-clockers » ou les horloges externes, que l’on voit apparaître pour tenter de palier aux insuffisances de la réjection du jitter des DACs traditionnels.

Technologie brevetée

Partant de ce constat, nous avons imaginé une technologie unique (brevet B.audio) qui permet d’éliminer totalement le jitter du signal numérique d’entrée : la technologie SJR (Source Jitter Removal).

Fondamentalement, le SJR allie les avantages des deux technologies classiques de limitation de la gigue d’entrée, sans toutefois en avoir les contreparties. En effet, l’horloge générée au sein du SJR ne régénère aucune composante du jitter source, et les données numériques ne sont pas altérées au sein de ce procédé.

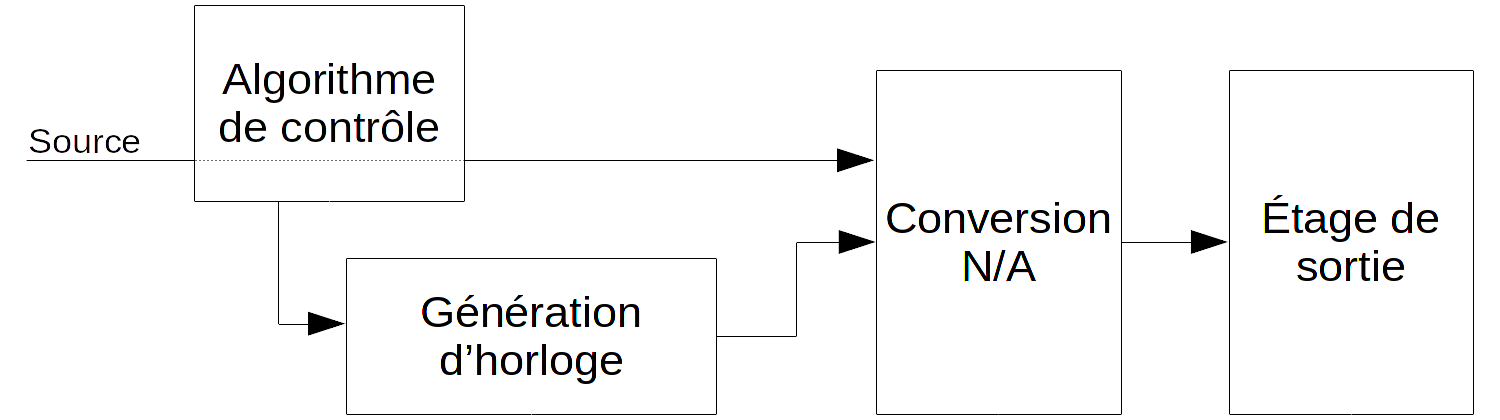

Il opère selon le schéma suivant :

Principe de fonctionnement

Un signal d’horloge dénué d’impuretés et complètement découplé du signal d’entrée est recréé, fournissant un timing optimal pour la conversion numérique/analogique. Etant complètement décoréllé du signal d’entrée, il ne contient pas de composante résultant du jitter source.

Le SJR est 100 % effectif, quelle que soit la source (SPDIF, Toslink, AES/EBU, USB), sans nécessiter de recourir à un signal d’horloge externe (entrée/sortie masterclock).

Un signal « bit perfect »

Comme les échantillons numériques ne sont pas modifiés par ce procédé, ils ne contiennent pas non plus de traces du jitter source.

Couplé aux étages de sortie symétriques hautes performances de nos convertisseurs, cette technologie permet de supprimer efficacement les duretés présentes classiquement lors de la lecture des formats numériques.