Rethinking the digital input stage of our converters, we developed a process that completely eliminates the source jitter. By enabling conversion circuits to work optimally, the SJR ensures unprecedented digital-to-analog conversion quality, regardless of the digital input format.

ELIMINATING JITTER AT THE SOURCE

The jitter contained in the input signal is a source of distortion during the digital-to-analog conversion, due to a time reference shift between each sample.

The need for a new concept

To avoid this phenomenon, two different technologies are usually employed: The use of PLLs (phase-locked loops) or the use of asynchronous resamplers (ASRC).

Although these two technologies attenuate the influence of the source jitter, they cannot completely eliminate it. With the use of a PLL, part of the source jitter is embedded in the generated clock; with the use of an ASRC, part of the source jitter is encoded in the resulting digital signal.

Other tricks can be used to improve jitter rejection, such as “re-clockers” or external clocks, which are now appearing in an attempt to overcome the shortcomings of jitter rejection in traditional DACs.

Patented technology

On the basis of this observation, we have developed a new unique technology (patented by B.audio) that allows the jitter to be completely eliminated from the digital input signal: the SJR (Source Jitter Removal) technology.

In essence, SJR combines the advantages of the two traditional input jitter mitigation technologies, but without having their trade-offs. Indeed, the clock generated within the SJR does not regenerate any component of the source jitter, and the digital data is not altered within this process.

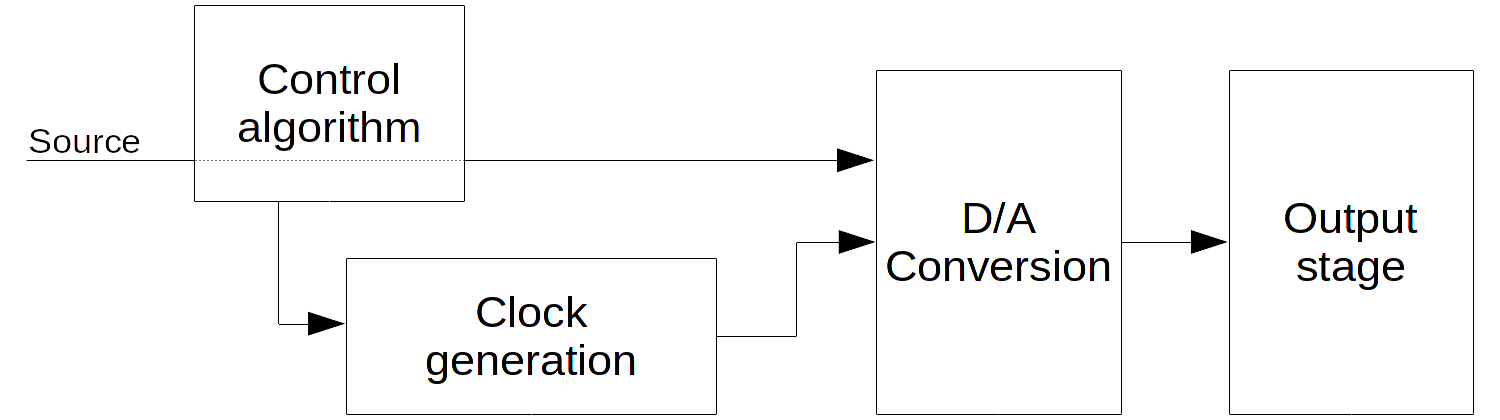

It operates according to the following scheme:

Principle of operation

A clock signal free of imperfections and fully decoupled from the input signal is recreated, providing optimal timing for digital-to-analog conversion. Being completely disconnected from the input signal, it does not contain any source jitter components.

The SJR is 100% effective, regardless of the source (SPDIF, Toslink, AES/EBU, USB), without the need for an external clock signal (masterclock input/output).

A “bit perfect” signal

Since the digital samples are not altered by this process, they do not contain any traces of the source jitter either.

Combined with the high-performance symmetrical output stages of our converters, this technology efficiently removes the hardness that traditionally occurs when reading digital formats.